DDR SDRAM

DDR SDRAM

特性

- SDRAM: synchronous dynamic random-access memor

- SRAM: Static random-access memor

- DRAM 存储采用单个电容比 SRAM采用晶体管面积更占优势(SRAM 1-4M)

- SRAM由于是芯片内部小电容掉电较快,需要cpu提供同步信号(synchronous)增加了控制器的复杂性

- DDR :Double Data Rate 提高内存速度

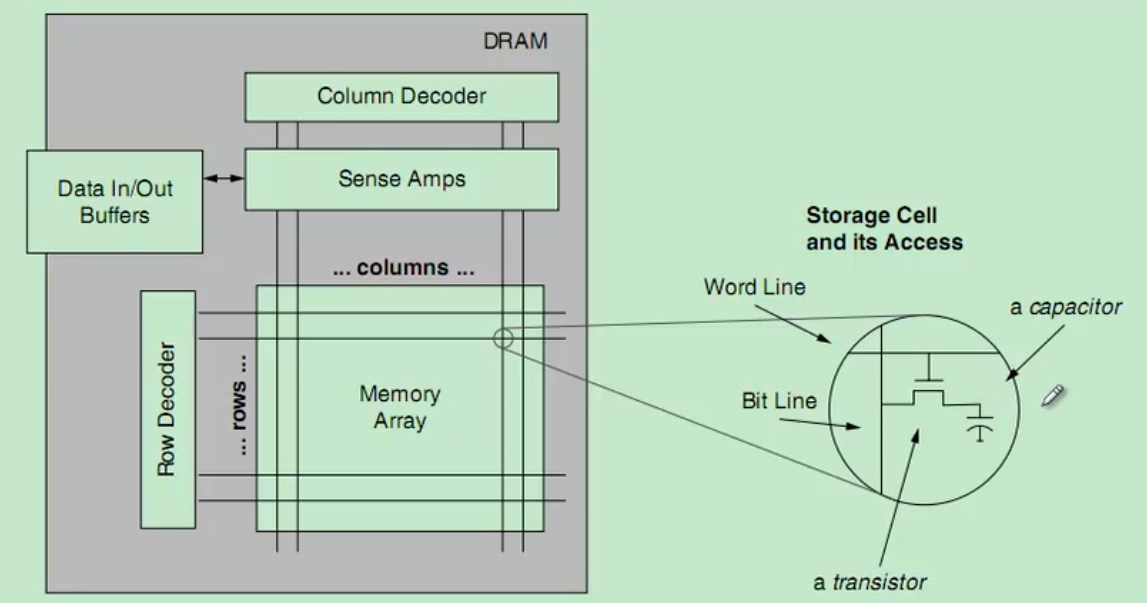

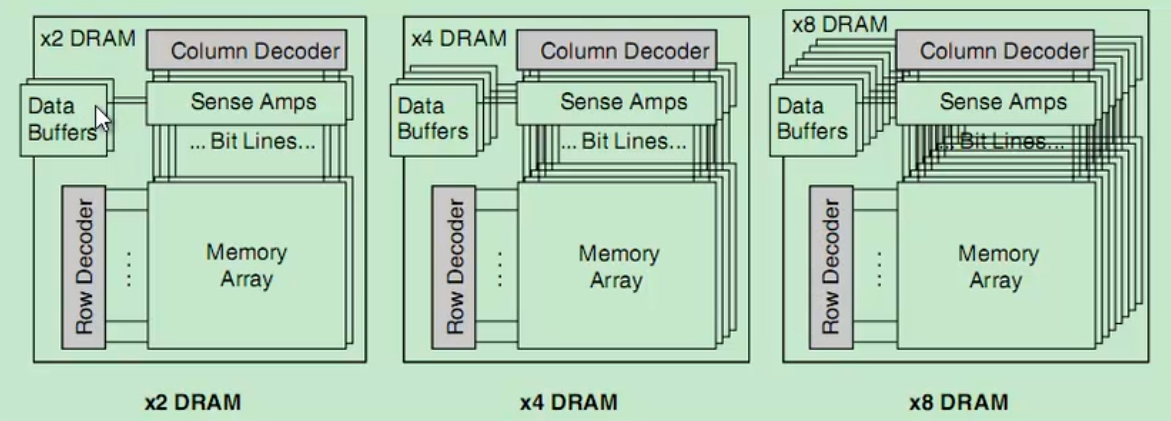

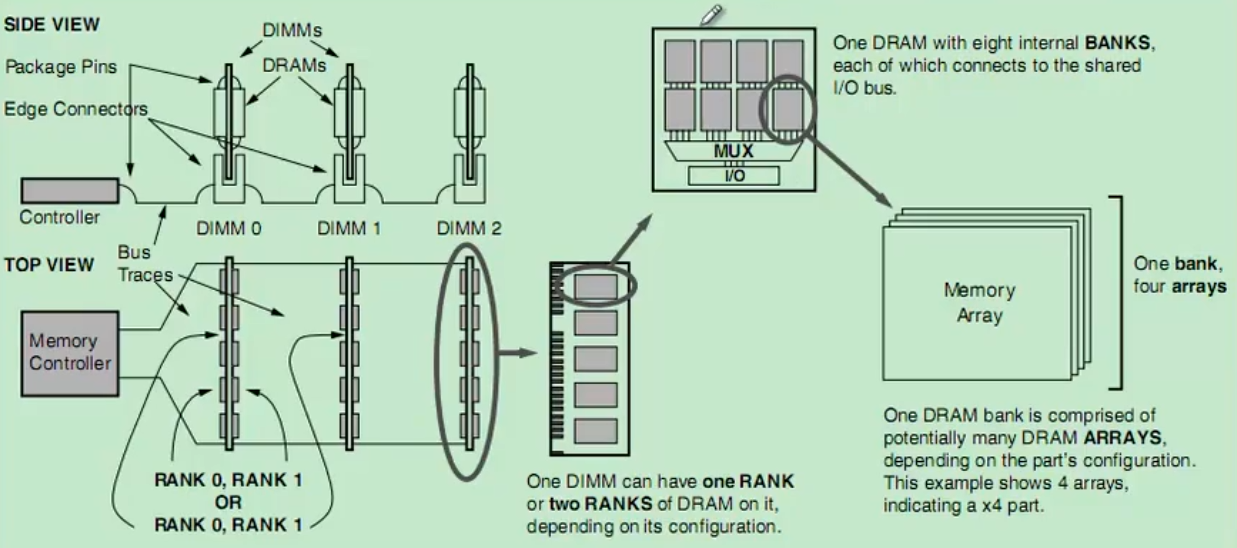

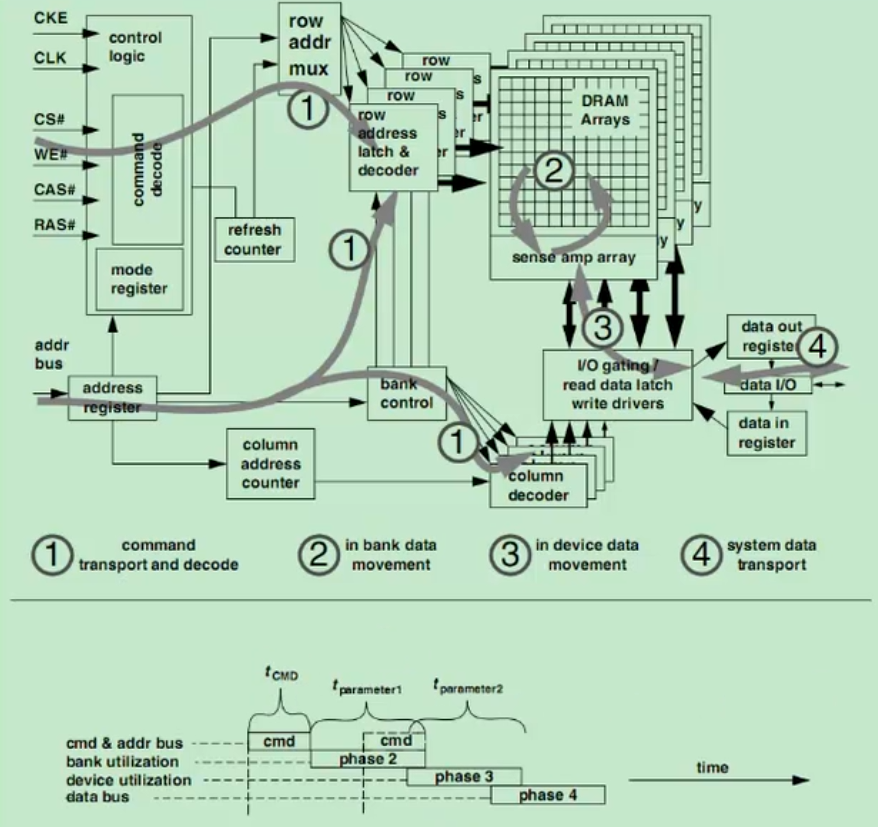

DRAM结构

组成:Array、Bank、Memory Device、Rank、DIMM(Dual in-line memory module)

Array

Bank

Memory Device、Rank、DIMM

多Bank目的是为了交叉充电

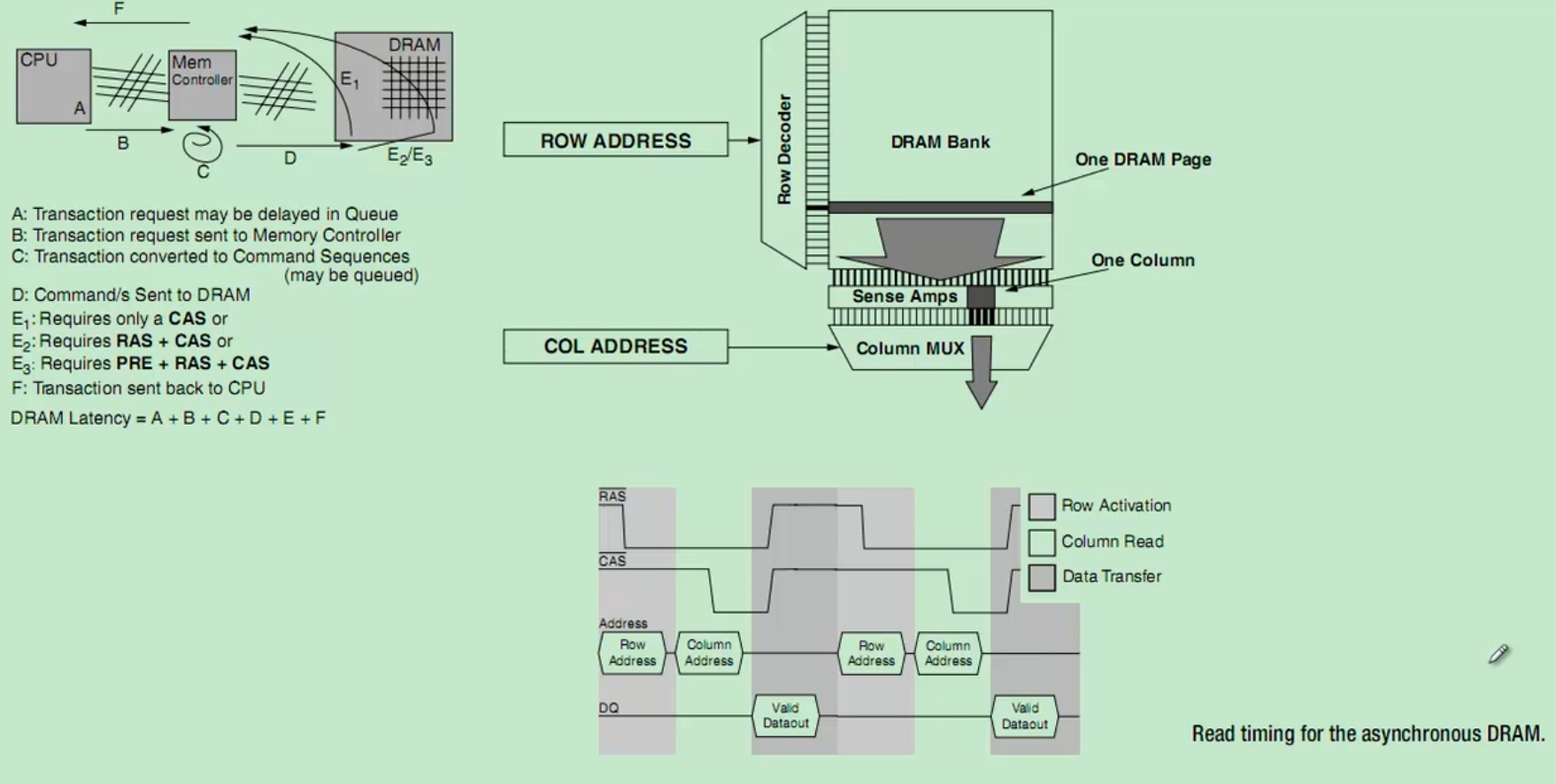

读写操作时序

CAS/RAS参数意义

- RAS: row address strobe

- CAS: column address strobe

- DQ:Data Bus数据线

- DM:Data Mask 当写入操作时,在DM信号有效时写入DQ数据。

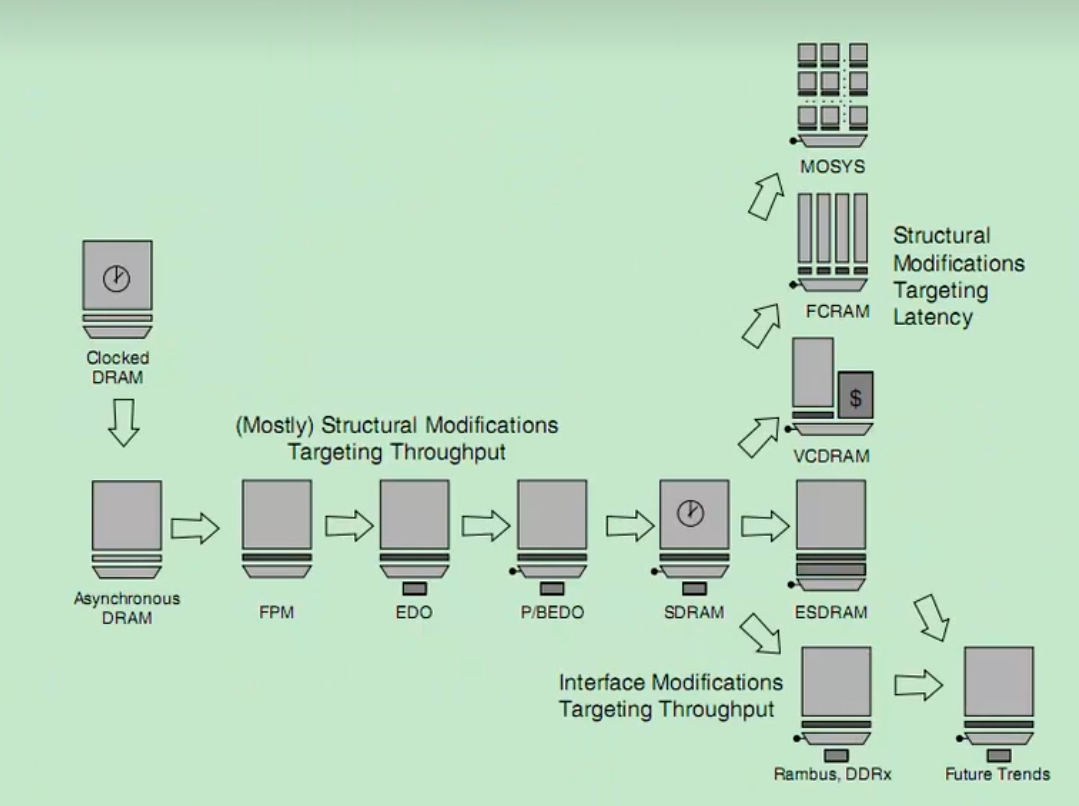

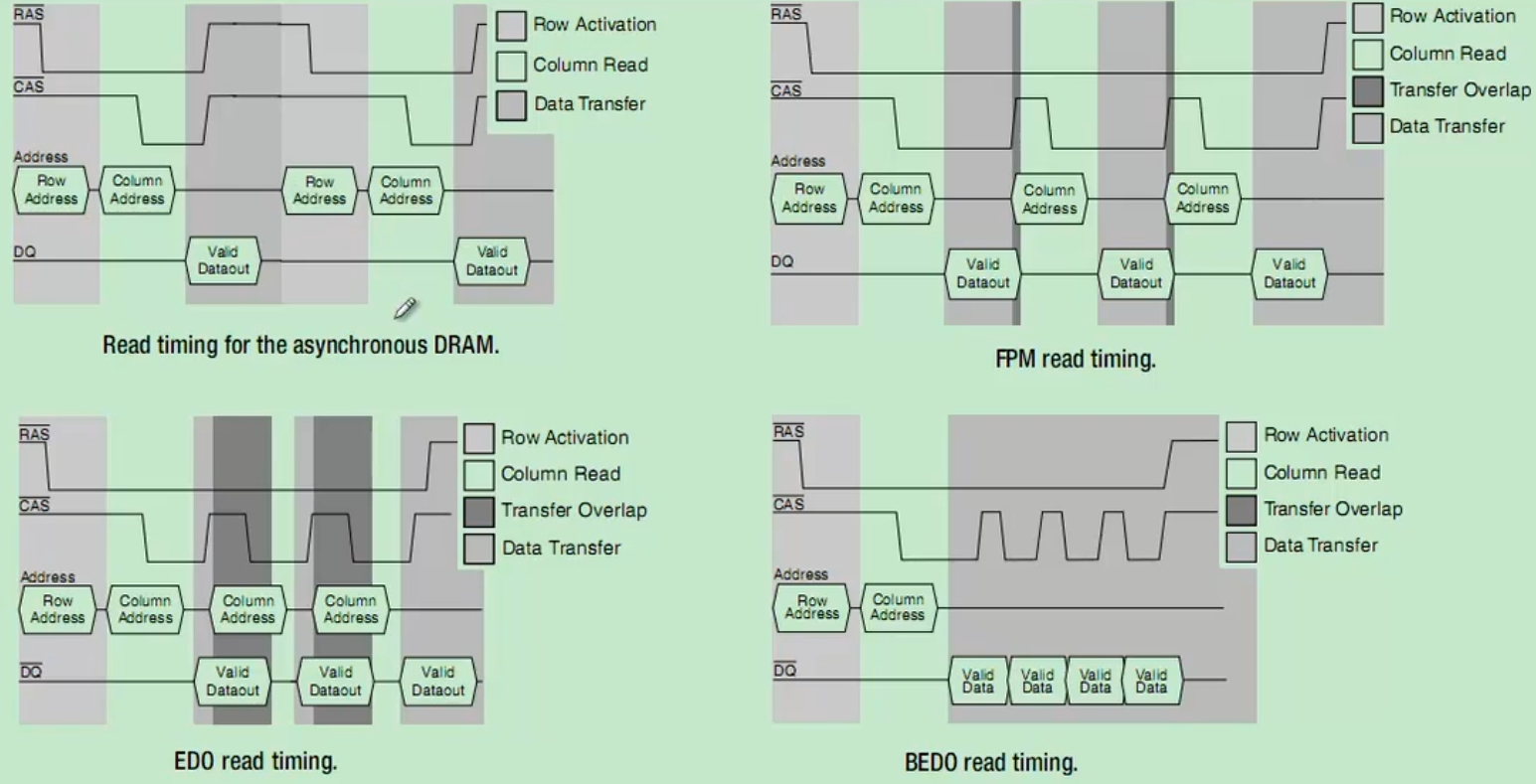

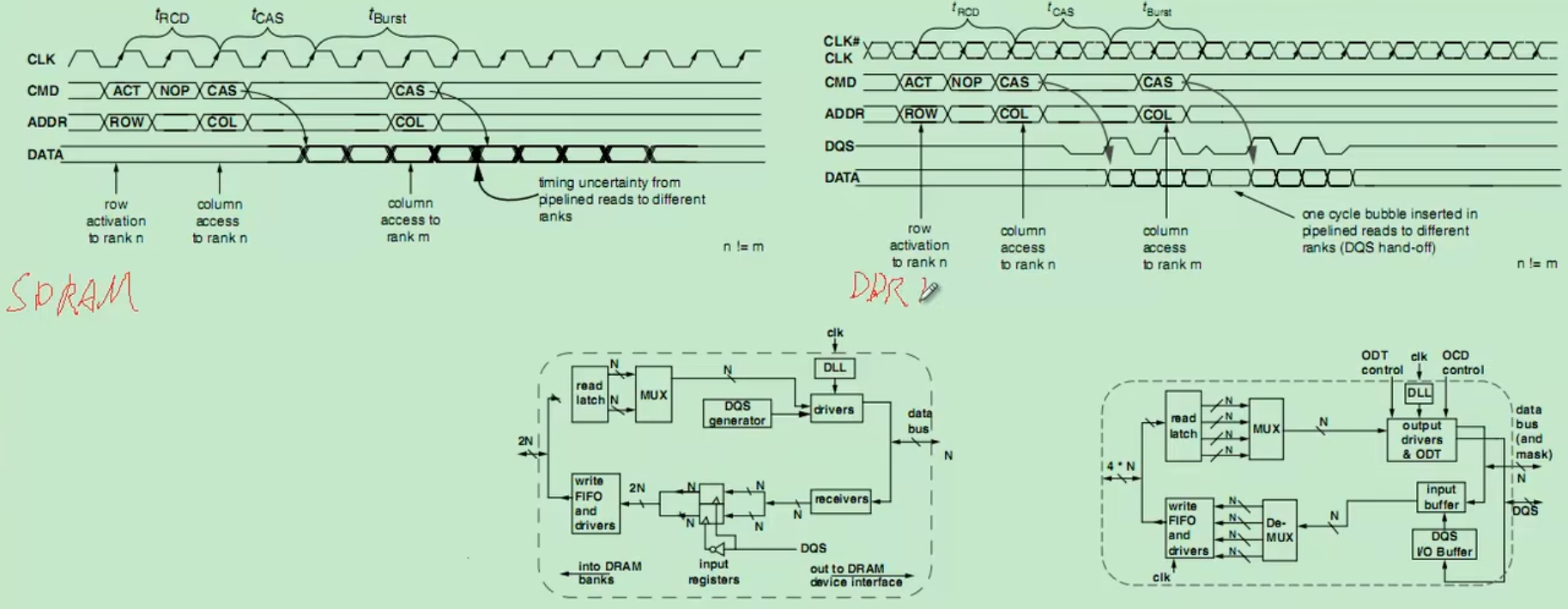

DRAM操作时许演变对比

FPAM:FAST Page Module 根据局部性原理,行地址不需要经常根本更换,速度翻倍

EDO:Extend Data Out 列地址和数据时间复用,速度翻倍

BEDO:Burst EDO 爆发时EDO模式,芯片内部添加累加器自动计算新地址,不需要每次都给列地址,节约了列地址解码时间,速度增长30%

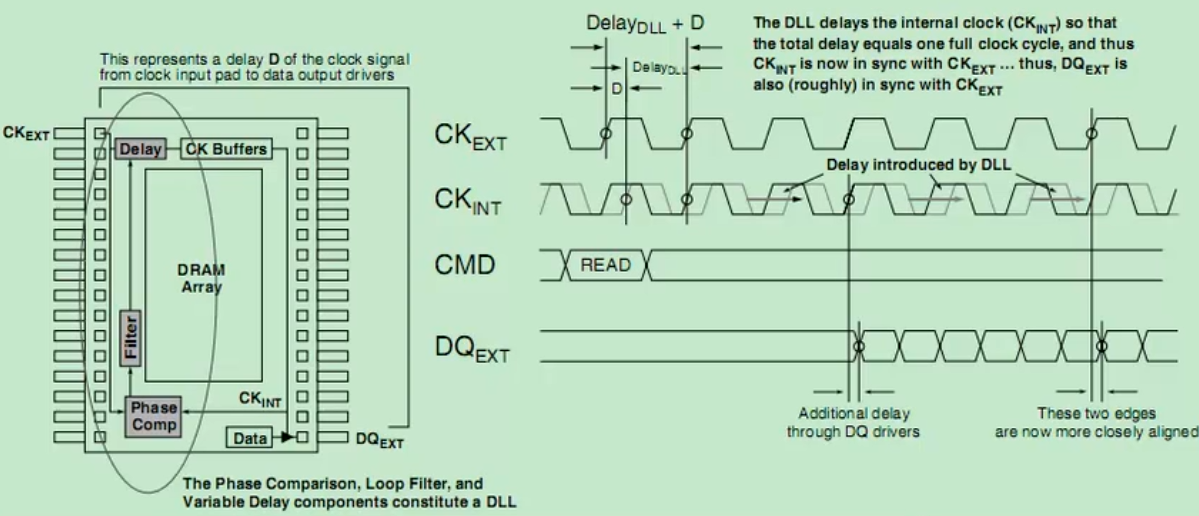

DLL:Delay Lock Loop 用于DDR外部引脚信号和内部信号不同步进行同步操作

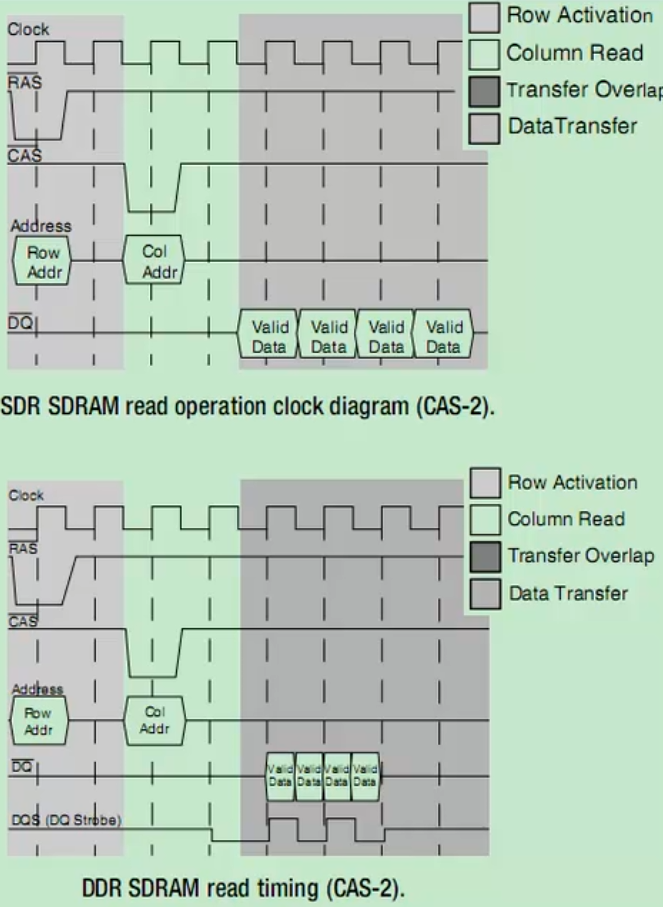

DDR Read

20世纪80年代,计算机发展迅速,出现内存和cpu速度不匹配情况,异步此时限制了内存速度的进一步提高,内存又重新回到了同步的通信方式,时钟信号的出现对速率并没有明显提升,但可以通过修改时钟频率提升了内存的适用性。

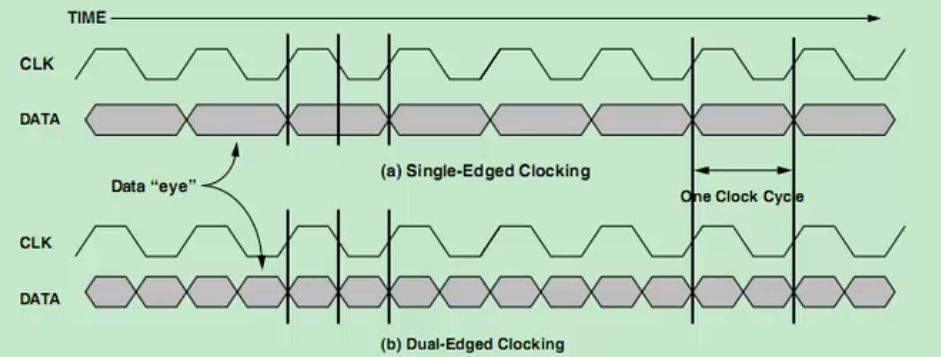

SDR:采用单个时钟信号传输数据

DDR:采用上升沿和下降沿传输数据,速度翻倍Dual/Duble

CAS-2: CAS到RAS延迟两个周期

DQS:toggle 读数据的时候进行反转,作用不大,和数据线同步

DDR Write

DQS:在DDR中通知芯片可以进行数据锁存,进行数据写操作,比数据线晚半个周期

DQS对应着DATA数据线,所以在芯片电路设计中,并不能复用

DQS 采用差分信号避免并行数据线中的干扰

CKE:时钟使能 nWE:读写操作标记 ODT:决定是否启动内部上下拉电阻降低频率高导致集电容效应影响信号质量

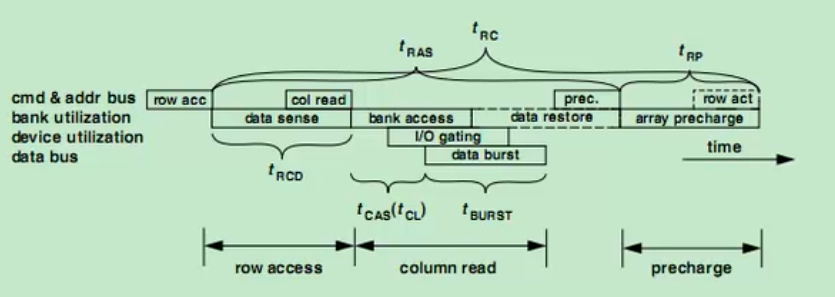

内存时序关键参数

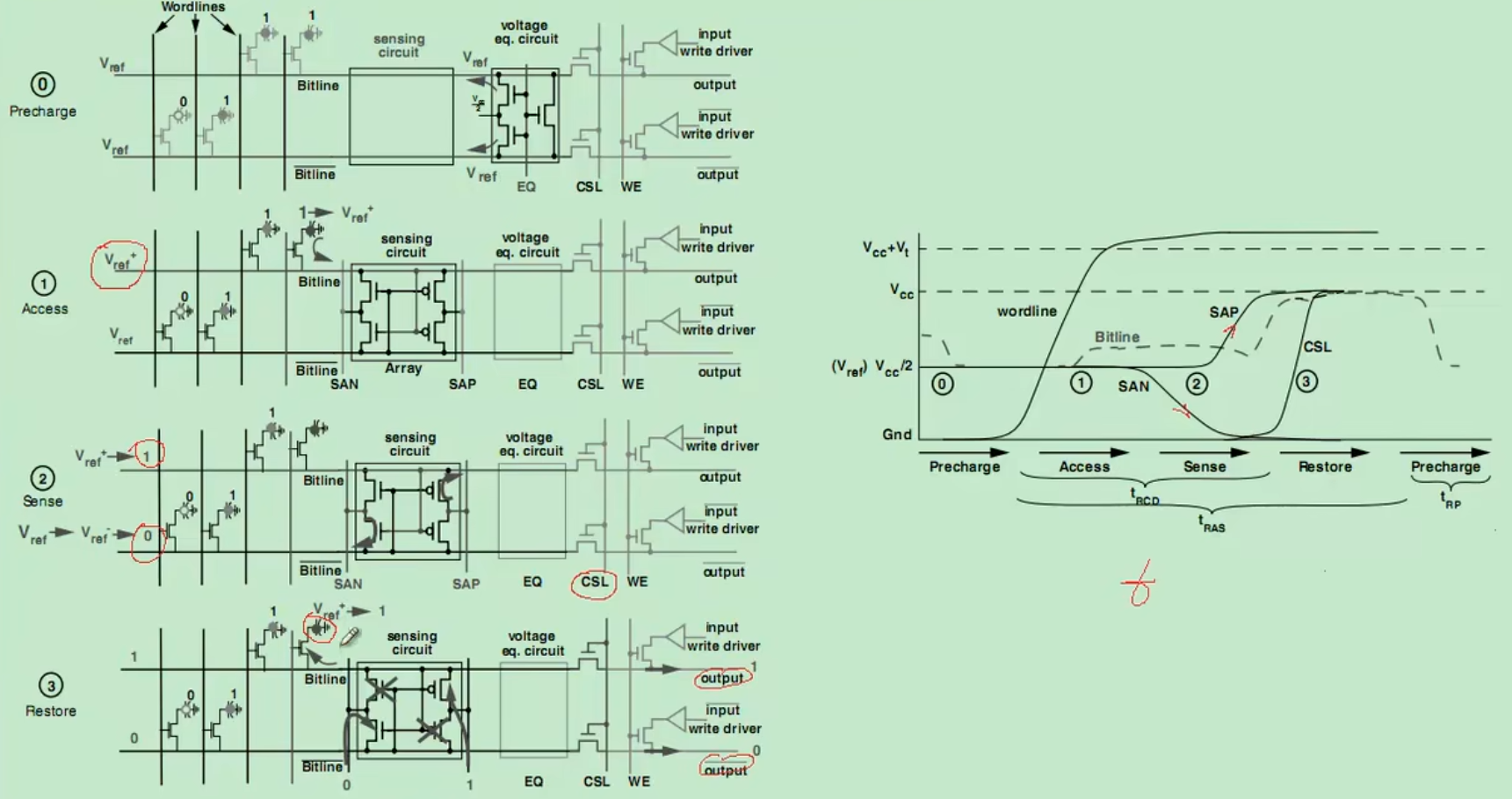

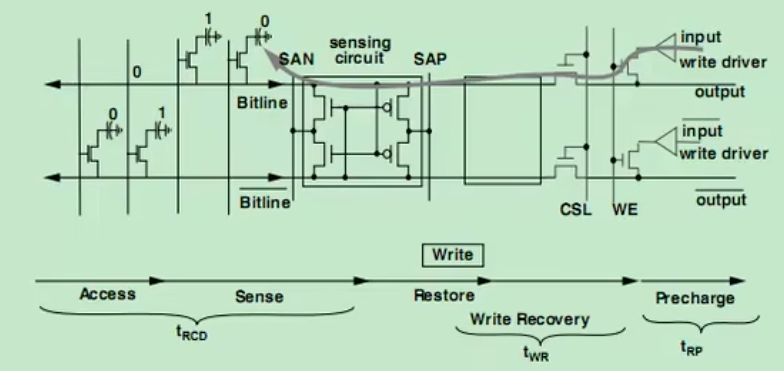

Read四个阶段

Precharge Access Sense Restore

Trcd: Row to Col Delay

Tras: Row access Stroke

Trp: Row Precharge

Write四个阶段

Access Sense Restore Precharge

Trcd:Row Column Delay

Twr:Write Delay

Trp: Row Precharge

SDR和DDR对比

DDR不断迭代过程频率不断提高,但其中控制逻辑的速度并没有提高(Trcd Tras没有显著改变),只是提高BANK读取的位数,拓展了带宽

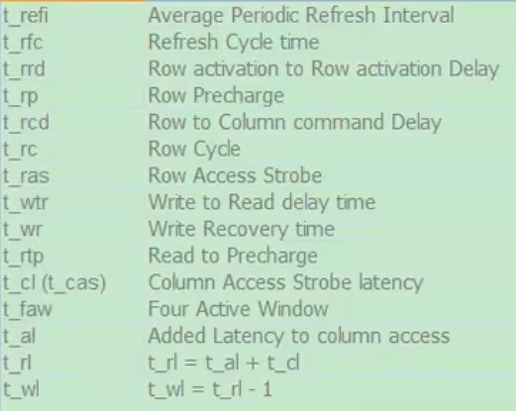

读写操作时间参数

read

write

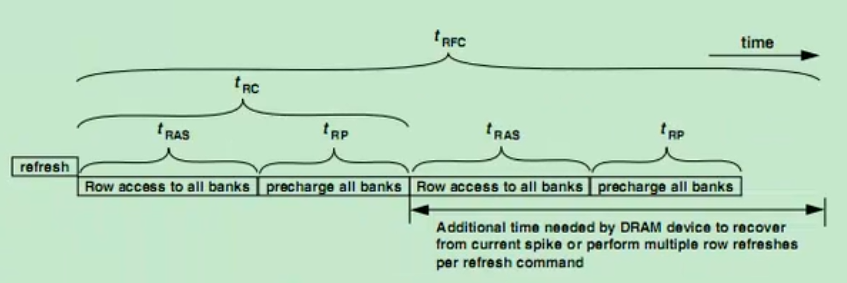

refresh

此处的Trc和读写的Trc不同,refresh会同时刷新多个行

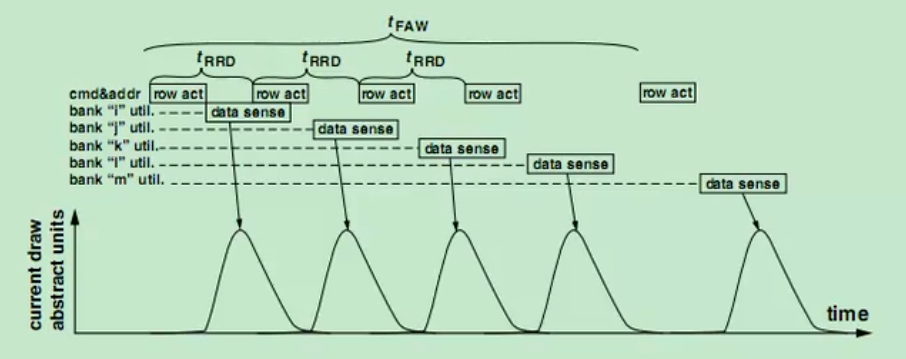

Trrd Tfaw

参数列表:

Trefi = bank最低刷时间/刷新bank行次数